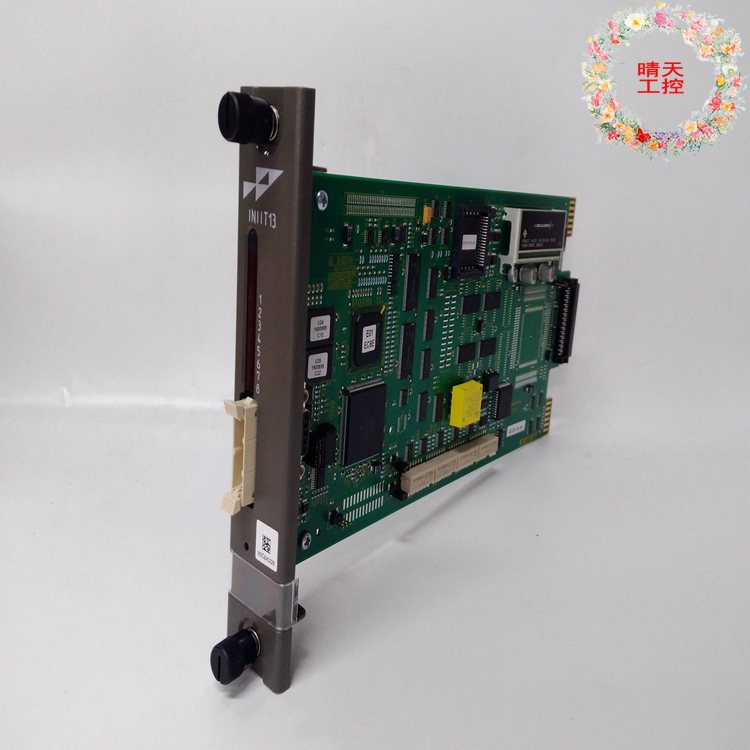

ABB INIT03 automation processor module

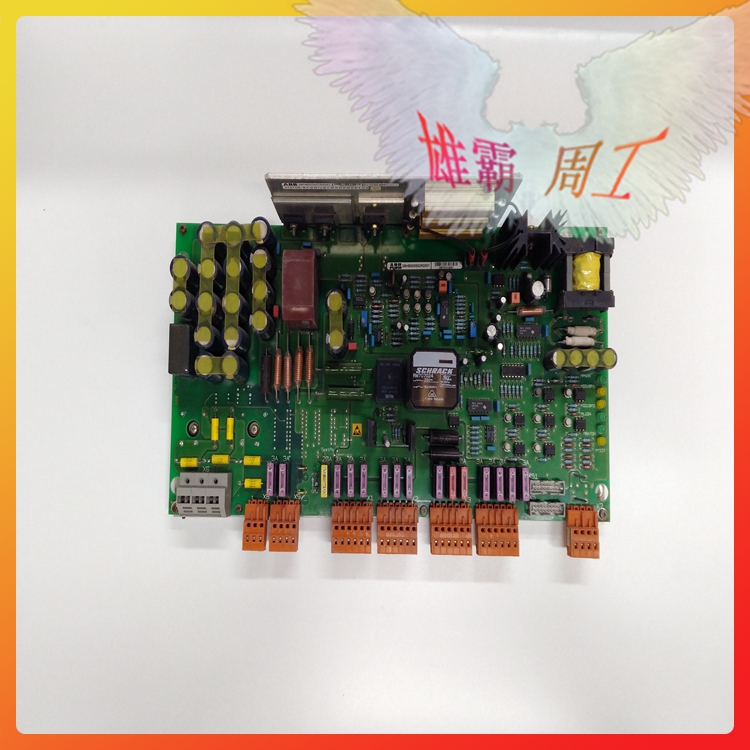

Brand ABB Color Standard Application Industrial height 346mm rated current 420mA

Protection Level IP45 Suitable for motor Power 479KW Applicable Site Power Industry BOM Number GJR2391500R1220 Power industry HIEE401782R0001 Part number INIT03

Applicable pipe 2 Whether imported is weighing 2.88 kg can be sold nationwide

ABB INIT03 automation processor module

The software design of the system can also be divided into two parts according to the overall division of the hardware structure. The operation of the whole system is shown in Figure 2. The programs of FPGA and DSP run independently and complete real-time data interaction through interrupt signals. The instruction from FPGA to DSP is to send an EDMA request through FPGA, and the DSP establishes an EDMA channel in response to the EDMA request and starts to read the pre-processed data from the FIFO. When the DSP transmits data to the FPGA, it sends an interrupt signal to the FPGA. Let it read the compressed image data out of the FIFO.

The whole system workflow can be simply described as follows: After the system is powered on, the DSP is bootstrapped by flash first, and the boot program is run, and then it is transferred to the EDMA waiting state. After initialization, the FPGA waits for the external image acquisition command. After receiving the image acquisition command, the image acquisition begins, and the acquired image is preprocessed. After storing a certain amount of data, FPGA sends EDMA request to DSP through half-full signal, waiting for DSP response. Once DSP receives EDMA request from FPGA, it immediately establishes EDMA channel, reads data from FIFO to L2 memory, and starts image compression after storing one frame of image. After an image compression is completed, the DSP sends an interrupt signal to the FPGA, and the FPGA begins to read the compressed image data from the FIFO after receiving the interrupt signal. After reading a frame of data, the encoded signal is judged whether it is valid. If it is valid, the next frame image is compressed according to the same rules. If it is invalid, the DSP is notified to end.

ABB INIT03 automation processor module

ABB TU804-1

ABB TU810V1

ABB XI16E1

ABB XM06B5

ABB XO16N1-B20 XO16N1-C3.0

ABB YB560100-EA S3

ABB YYT107A

ABB 07KT97H3

ABB 086329-003

ABB 086329-004

ABB 086345-504

ABB 086351-004

ABB 12KM02E-V0002

ABB 3BHB003154R0101

ABB 3BHB004027R0101

ABB 3BHE039203R0101

ABB 3HAB8101-19 DSQC545A

ABB 3HAB8859-1/03A

ABB 3HAB9271-1/01B

ABB 3HAC026271-001/DSQC646

ABB 3HAC031683-004

ABB 3HAC0977-1

ABB 3HAC10847-1

ABB 3HAC17484-8108

ABB 3HAC5497-1