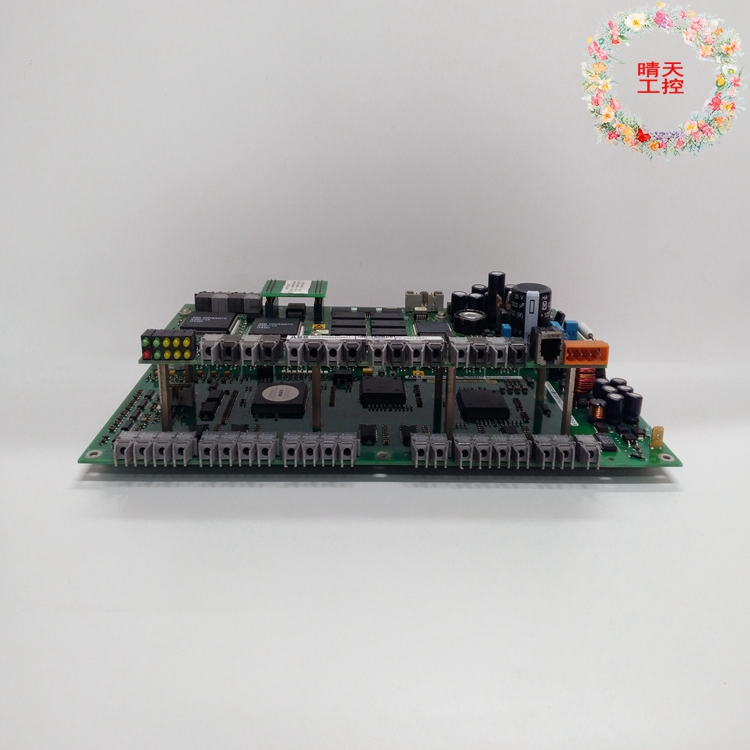

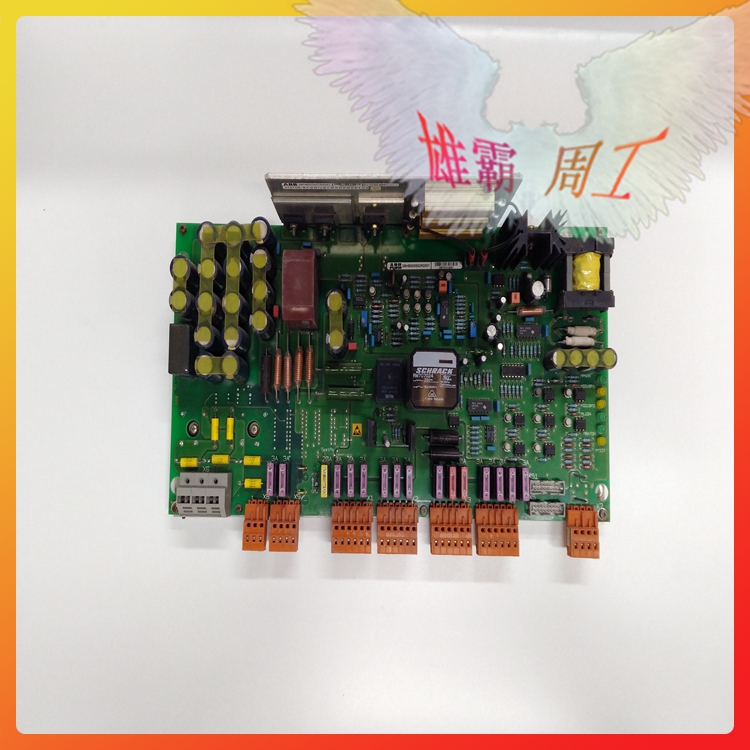

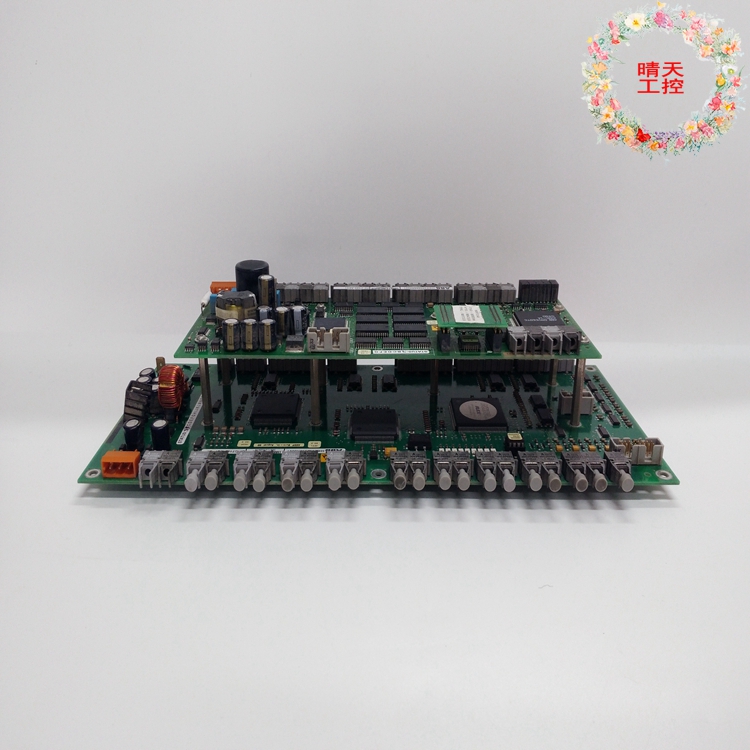

ABB distributed control system UFC718AE01 spare parts industrial DCS module card

Brand ABB color Standard Application Industrial height 228mm rated current 570mA

Protection Level IP45 Suitable for motor power 476KW Application Site Power Industry BOM Number GJR2391500R1220 Power industry HIEE401782R0001 Part Number UFC718AE01

Applicable pipe 2 Whether imported is weighing 3.88 kg can be sold nationwide

ABB distributed control system UFC718AE01 spare parts industrial DCS module card

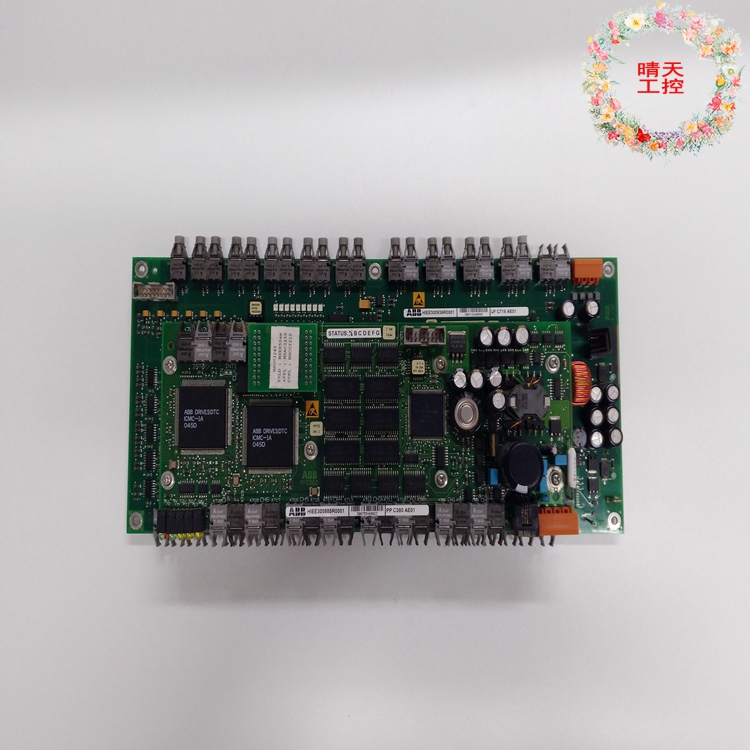

UFC718AE01 HIEE300936R0001 FPGA-based DDS circuit

2.1.1 Phase accumulator

For the design of DDS signal source using FPGA, the phase accumulator is a key part to determine the performance of DDS circuit. The phase accumulator is composed of an n-bit accumulator and an N-bit register cascade. For each clock pulse, the phase register samples the sum of the value of the phase accumulator and the frequency control word K in the previous clock cycle, and acts as the output of the phase accumulator in this clock cycle. As can be seen from formula (2), the larger the bit N of the phase accumulator, the smaller the frequency resolution, but at a higher operating frequency, a larger delay will be generated which cannot meet the requirements of speed. In sequential circuits, pipelining technology is usually used to improve speed, at the cost of increasing the number of registers, which accounts for more data in FPGA. Overall consideration, the use of 32-bit accumulator, four-stage pipeline structure.

2.1.2 Phase-amplitude converter

The phase-amplitude converter is composed of ROM, which converts the digital phase information of the output of the phase accumulator into a sine wave value. In FPGA, ROM is generally implemented by EAB, and the size of ROM table increases exponentially with the address bits or data bits, so the design of phase-amplitude converter is another key to affect the performance of DDS, which is mainly to reduce resource overhead under the premise of meeting the requirements of signal design indicators. Considering that this design only needs to output sinusoidal signal, sine wave signal about the point (π, 0) odd symmetry, only need to store 1/2 cycle waveform data, and according to the left half cycle, waveform about the line x=π / 2 even symmetry, so only need to store 1/4 cycle sine function value, you can get the whole sine code table through appropriate transformation. This saves three quarters of the resources.

2. 2 Low-Pass filtering module

DDS has an obvious disadvantage, that the closer the output frequency is to the high end of the Nyquist bandwidth, the fewer the sampling points, and the greater the stray interference of its output. The output waveform has a lot of harmonic components and system clock interference. In order to obtain the signal in the required frequency band, it is necessary to add a filter to the output end of DDS, and the low-pass filter can better filter the clutter and smooth the signal, so the design of the low-pass filter is particularly important, and the filter characteristics have an important impact on the performance of the output signal.

In order to achieve a better filtering effect, the filter is segmented by a four-choice analog switch and a precision operational amplifier: Butterworth active low-pass filter is adopted, the amplitude of the filter is very flat, and the filter circuit is a second-order Butterworth low-pass filter circuit. The selection of filter frequency band parameters is realized by nINH, S0, S1 control signal output by FPGA to control the gating of analog switch.

2.3 Amplitude control

In this design, the amplitude control circuit adopts the digital control method to adjust the DAC reference voltage, and adopts two D/A cascades. The digital-to-analog converter DAC2 adopts an external variable reference source to change the output full amplitude current value by changing the value of the reference source. The variable reference source is generated by DAC1. The reference voltage of DAC1 is provided by a precision voltage reference chip with output voltage of 1.25V. If the amplitude output word of DAC1 is N1, the reference voltage of DAC1 is

If the digital input word of DAC2 is N2, the output voltage after current/voltage conversion is

2.4 Human-computer interaction

In order to control the frequency word input and amplitude control of DDS conveniently and quickly, this design uses a single chip computer to control the DDS signal generator. DDS has many frequency word and amplitude data word bits, while the output port bits of the MCU are limited, so the communication between the MCU and the FPGA adopts Serial Peripheral Interface (SPI) mode, and the MCU transmits the control command word to the FPGA. At the same time, in order to facilitate the input control, the keyboard and display system are added.

3. Realization of digital closed-loop control system

The designed excitation constant current source mainly provides excitation power for magnetic measuring instruments, so its accuracy and stability are required to be high, and the control strategy of current control is adopted to carry out closed-loop control. The structure block diagram is shown in Figure 3. When the excitation current amplitude is adjusted, the multi-period sampling of the excitation current is first carried out, and then the effective value is calculated, and compared with the input set value. If the error ε is outside the allowed range, a new control quantity is obtained according to the actual situation of the error through the incremental PID algorithm in the single chip microcomputer, and the control amplitude is adjusted by the low-pass filter to filter out the high frequency components. After power amplification, high precision excitation current is obtained.

ABB distributed control system UFC718AE01 spare parts industrial DCS module card

ABB 3BHB004027R0101

ABB 3BHE039203R0101

ABB 3HAB8101-19 DSQC545A

ABB 3HAB8859-1/03A

ABB 3HAB9271-1/01B

ABB 3HAC026271-001/DSQC646

ABB 3HAC031683-004

ABB 3HAC0977-1

ABB 3HAC10847-1

ABB 3HAC17484-8108

ABB 3HAC5497-1

ABB 3HAC5498-1

ABB 3HAC5518-1

ABB 3HAC5566-1

ABB 3HAC6157-1

ABB 3HAC6428-1/04

ABB 3HAC7344-1

ABB 3HAC7681-1

ABB 3HAC9710-1

ABB 5360673-01

ABB 57160001-KX

ABB 5SDD1060F0001

ABB 5SDF0860H0003

ABB 5SGY3545L0003

ABB 5SGY3545L0017