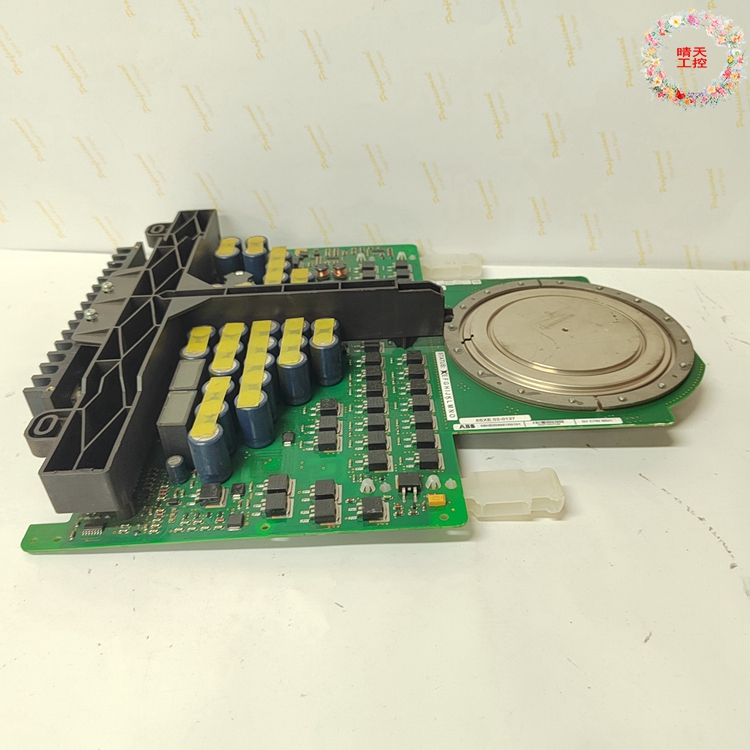

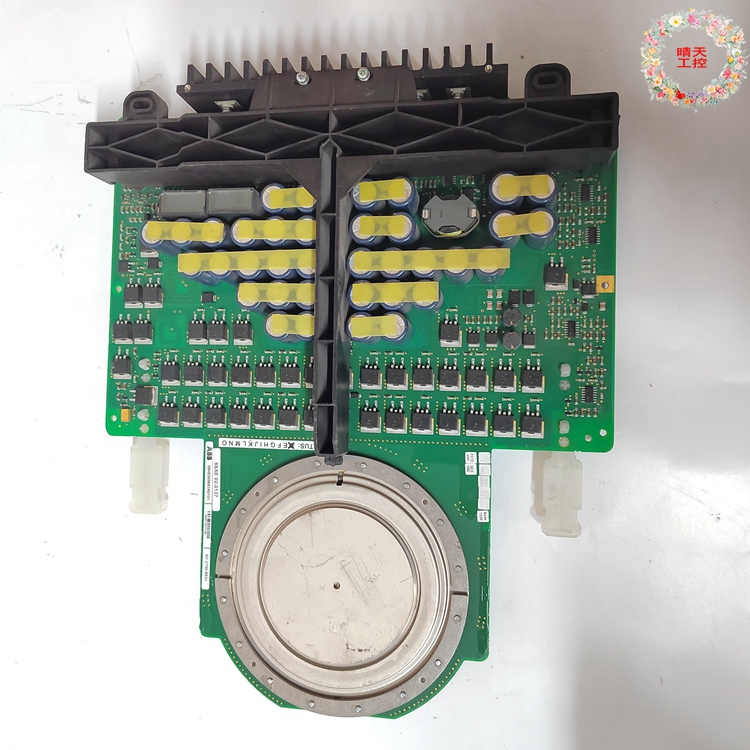

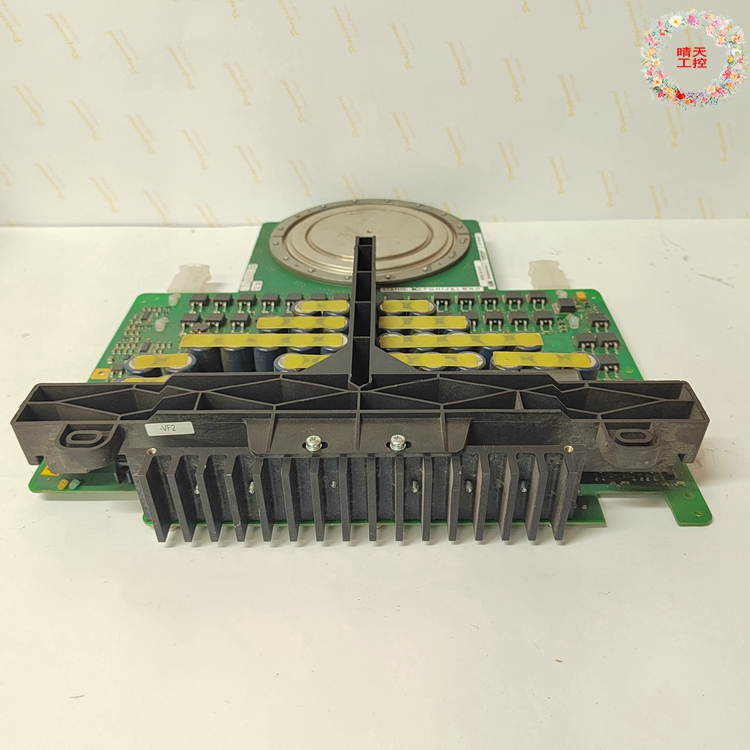

ARCOL 0346 Pressure guided load cell ABB

Brand ABB Color Standard Application Industrial height 265mm rated current 490mA

Protection Level IP45 Suitable for motor power 358KW Applicable Site Power Industry BOM Number GJR2391500R1220 Power industry HIEE401782R0001 Part Number ARCOL 0346

Applicable pipe 2 Whether imported is weighing 4.78 kg can be sold nationwide

ARCOL 0346 Pressure guided load cell ABB

ABB ARCOL 0346 seeks to increase the rate at which instructions are executed within the CPU

The description of the basic operations of a CPU in the previous section of ARCOL 0346 describes the simplest form that a CPU can take. This type of CPU, often called a subscalar, operates on one or two pieces of data at a time and executes one instruction, that is, less than one instruction per clock cycle (IPC %3C 1).

ARCOL 0346 This process leads to the inherent inefficiency of sub-scalar cpus. Since only one instruction is executed at a time, the entire CPU must wait for that instruction to complete before it can execute the next instruction. As a result, the child scalar CPU is “suspended” on instructions that require more than one clock cycle to complete execution. Even adding a second to the actuating part (see below) doesn’t improve performance much; Now instead of one path being suspended, two paths are suspended, and the number of unused transistors increases. In this design, the CPU’s execution resources can only process one instruction at a time and can only achieve quantitative performance (one instruction per clock cycle, IPC = 1). However, performance is almost always subscalar (less than one instruction per clock cycle, IPC %3C 1).

Attempts to implement scalars and better performance have led to a variety of design approaches that make the behavior of the CPU less linear and more parallel. When it comes to parallelism in cpus, two terms are commonly used to classify these design techniques:

Instruction level parallelism (ILP), which seeks to increase the rate at which instructions are executed within the CPU (i.e., increase the use of on-chip execution resources);

Task-level parallelism (TLP), the purpose of which is to add lines or processing cpus can execute simultaneously.

Each method is different in how they are implemented, and their relative effectiveness in improving the CPU performance of an application

One of the easiest ways to increase parallelism in ARCOL 0346 is to start the first step of instruction fetching and decoding before the previous instruction has finished executing. This technique is called instruction pipelining and is used in almost all modern general-purpose cpus. Pipelining allows multiple instructions to be executed at once by dividing the execution path into discrete stages. This separation can be likened to an assembly line, in which an instruction becomes more complete at each stage until it exits the execution pipeline and retires.

ARCOL 0346 Pressure guided load cell ABBABB DSPC454

ABB DSQC332A

ABB DSQC504

ABB DSQC509

ABB DSQC633

ABB DSRF197K01

ABB DTCC901B

ABB DTDX991A

ABB FPX86-9329–C

ABB GCC960C102

ABB GCC960C103

ABB GDC801B101

ABB HAC319AEV1

ABB ICSI16E1

ABB IMASI23

ABB IMBLK01

ABB IMDS014

ABB IMDSI14

ABB IMDSM04

ABB IMFECI2

ABB INIIT03

ABB INIIT13

ABB INIT03

ABB INNIS21

ABB INNPM12

ABB KUC720AE

ABB KUC720AE01

ABB MSR04X1

ABB MVR 0.44-10KA

ABB NPCT-01C

ABB PCD244A101

ABB PDD200A101